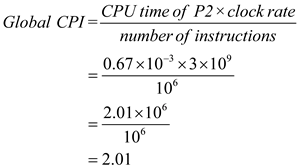

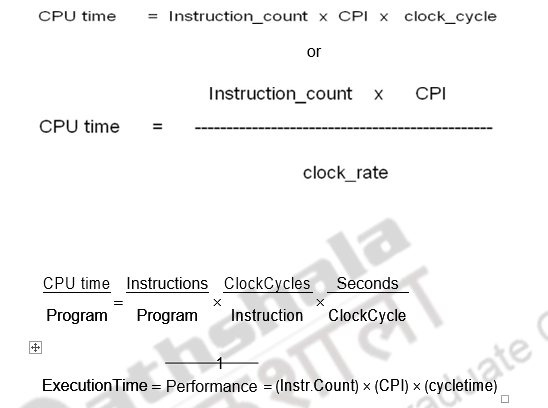

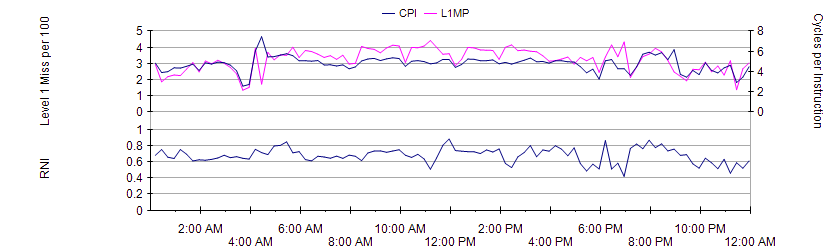

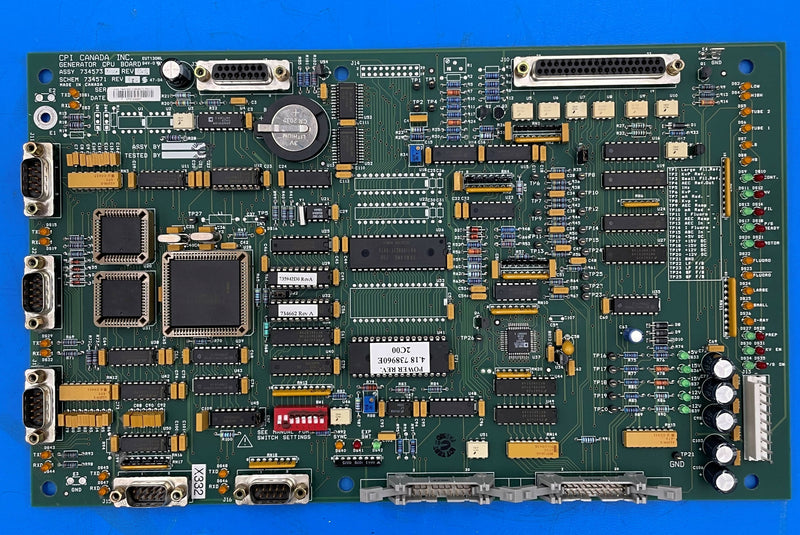

VLSI System Design - Fallacy - Higher the CPU frequency, faster the computer.... Below image, which is a snippet from my upcoming "RISC-V processor design course" on VSD, is a counter example

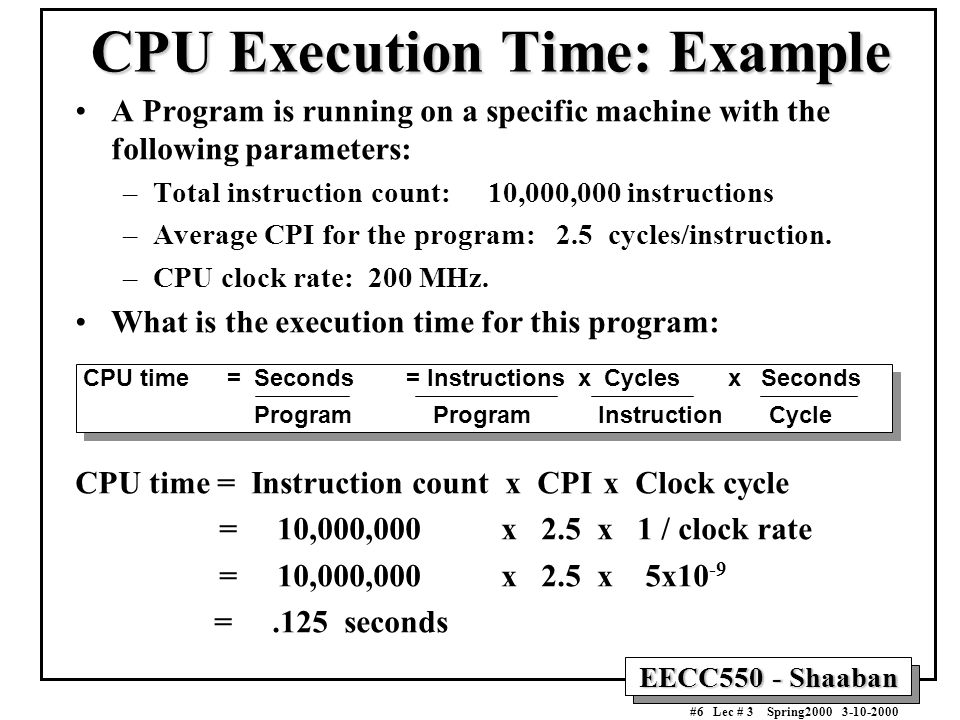

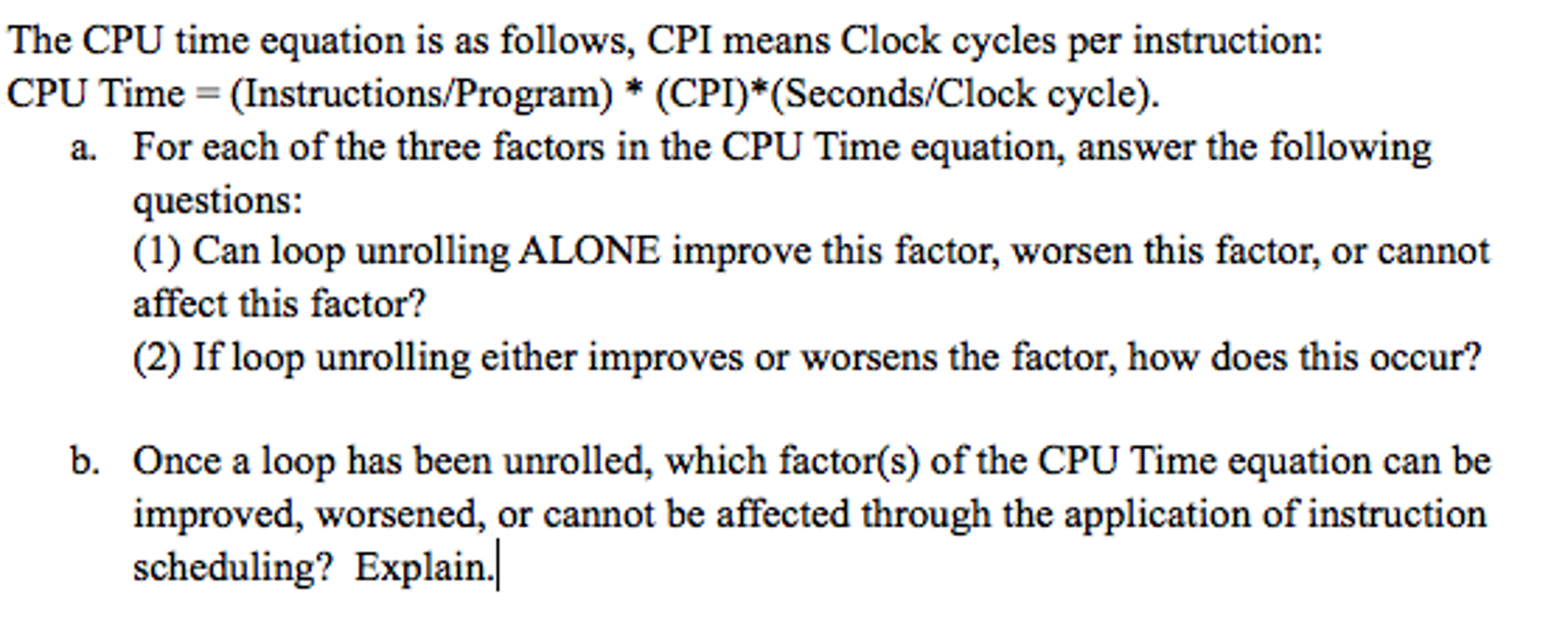

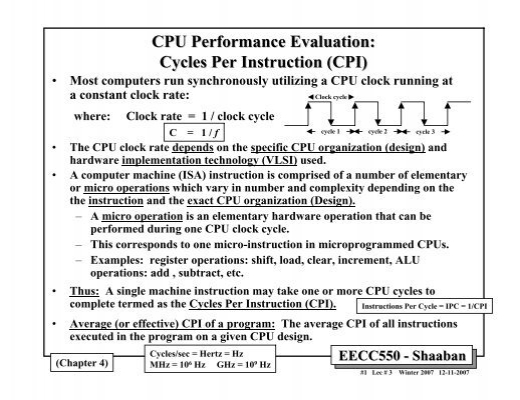

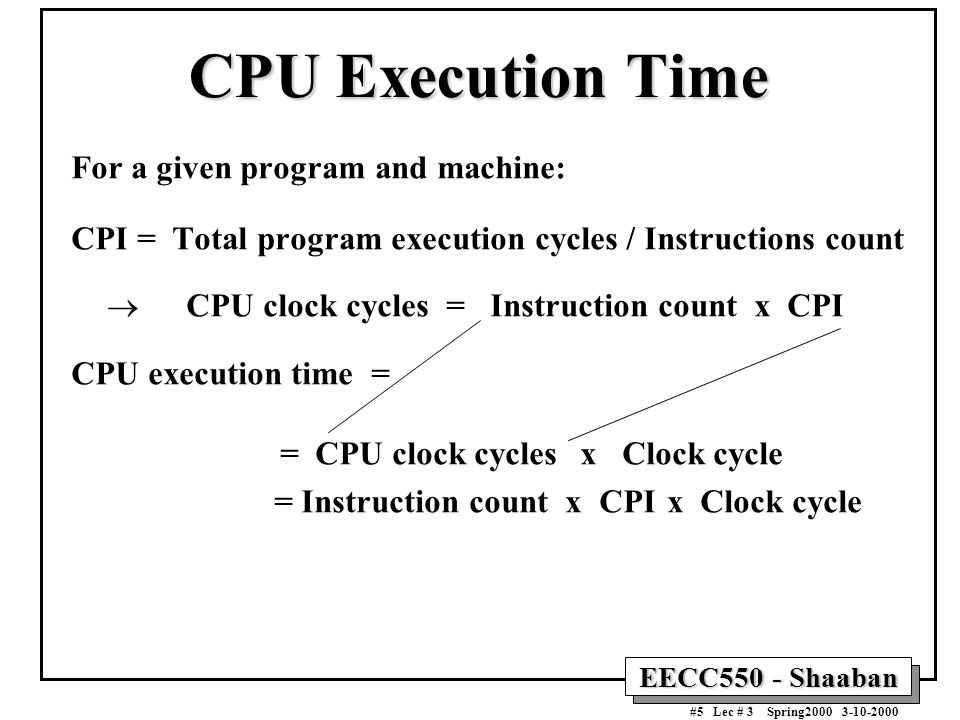

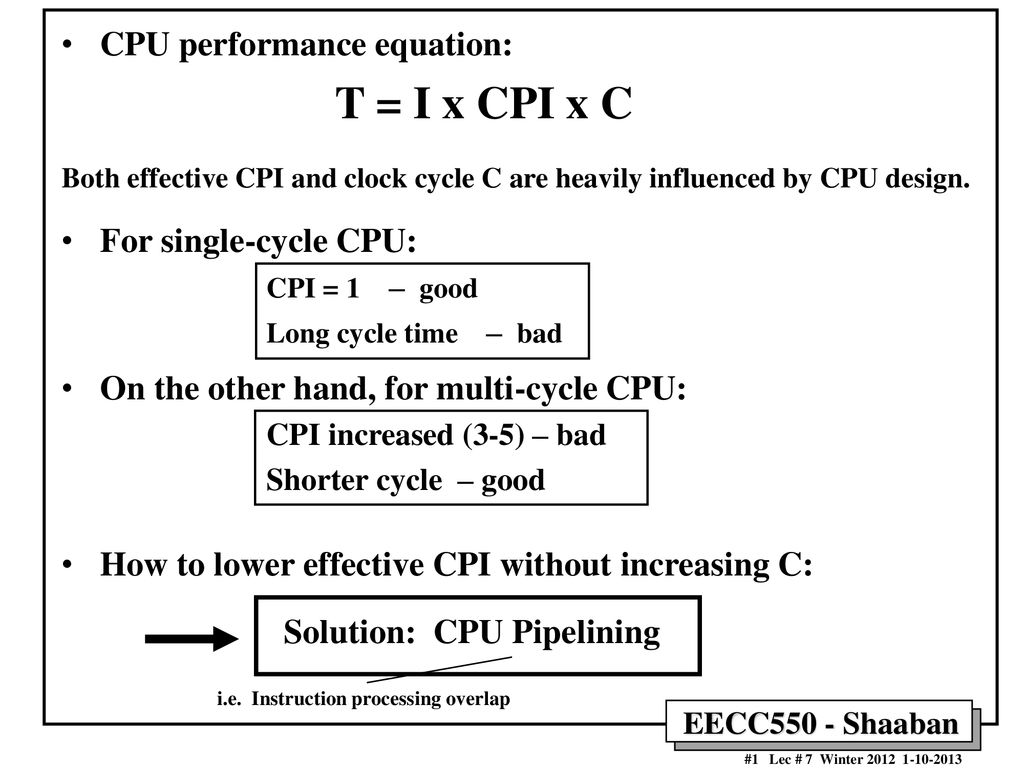

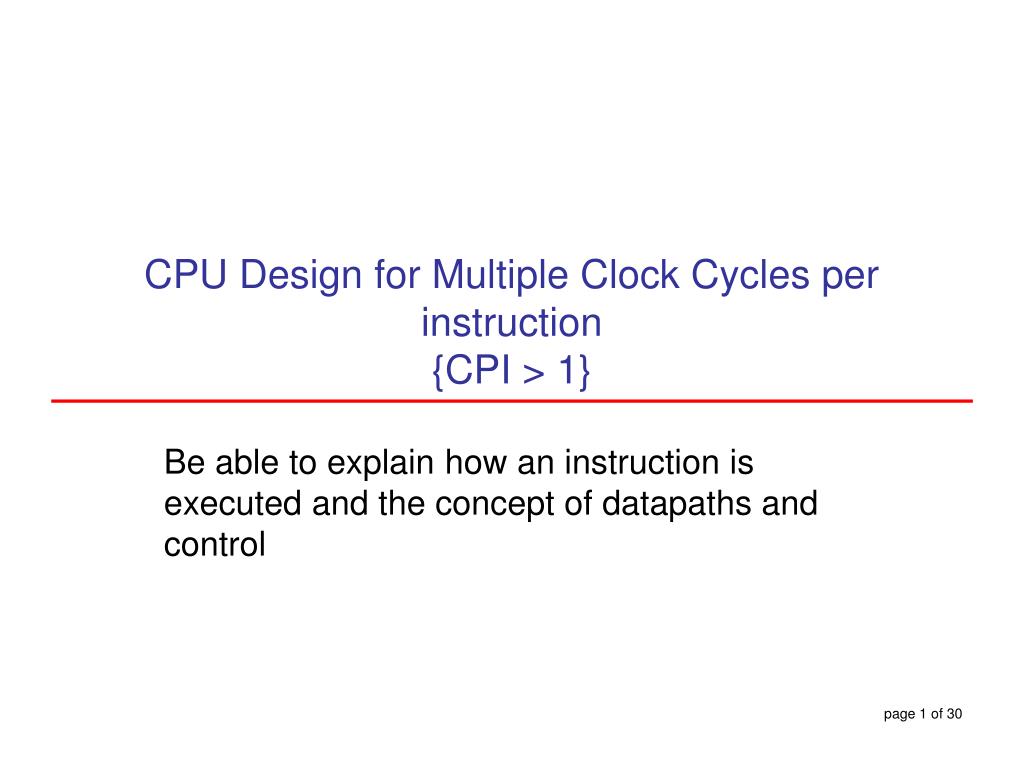

PPT - CPU Design for Multiple Clock Cycles per instruction {CPI > 1} PowerPoint Presentation - ID:6392146

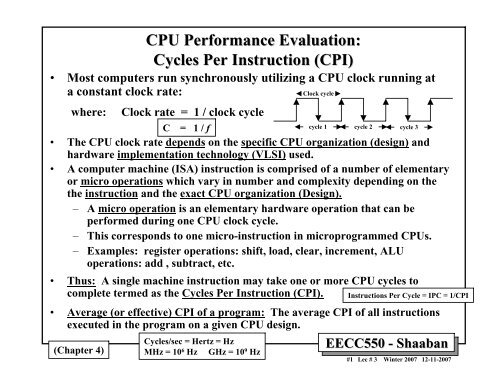

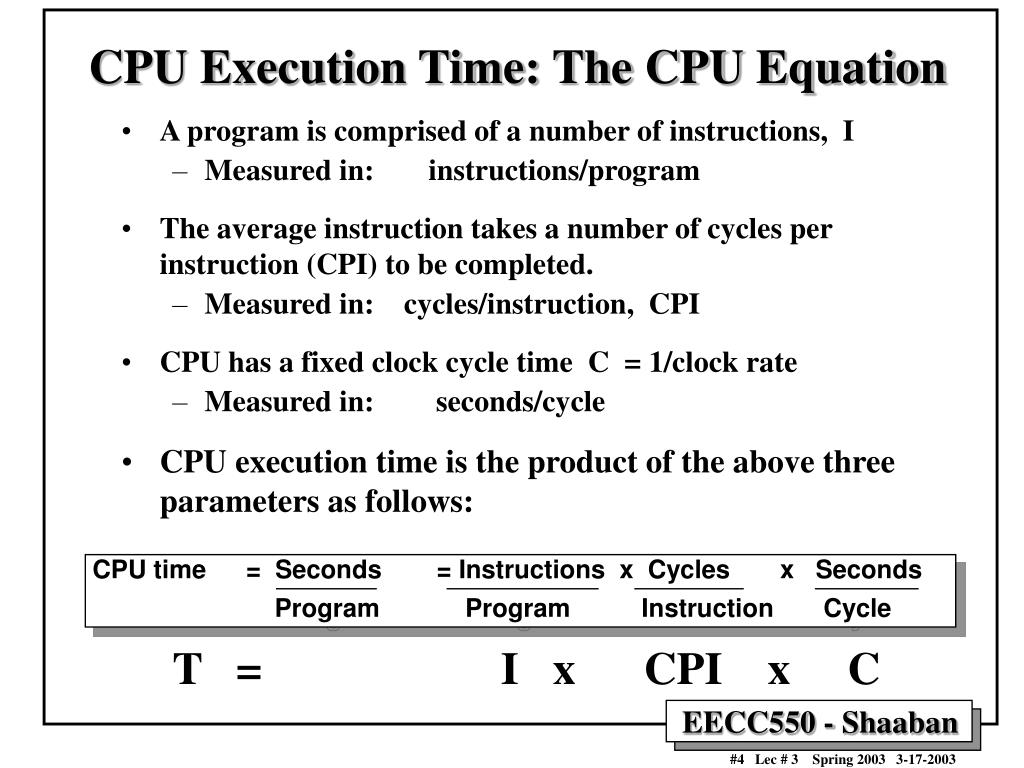

CPU Performance Evaluation: Cycles Per Instruction (CPI) Most computers run synchronously utilizing a CPU clock running at a constant clock rate: - PDF Free Download

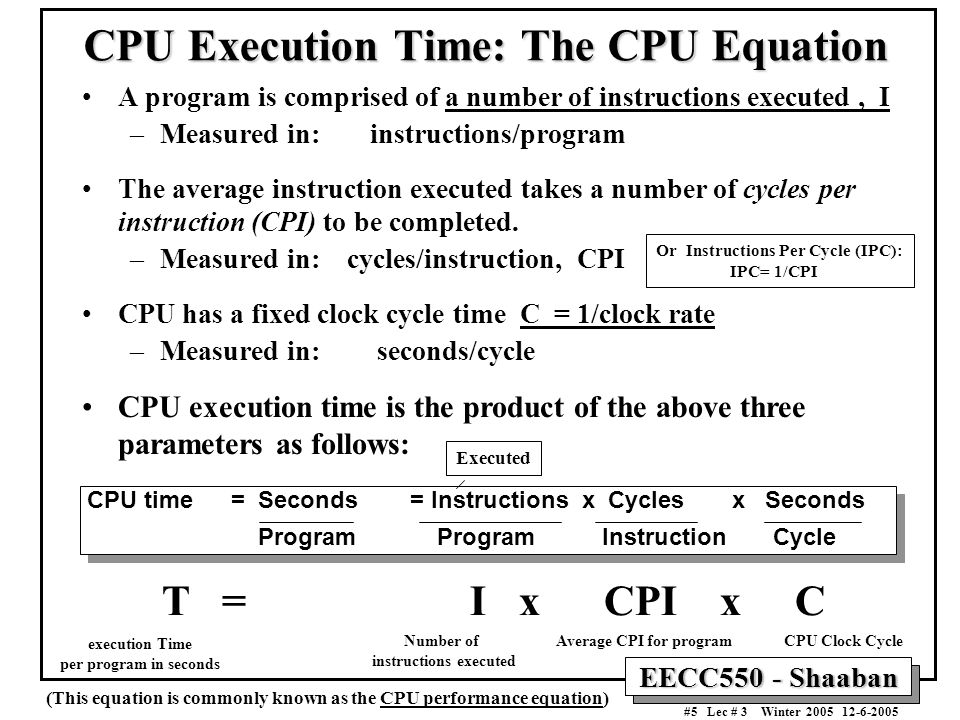

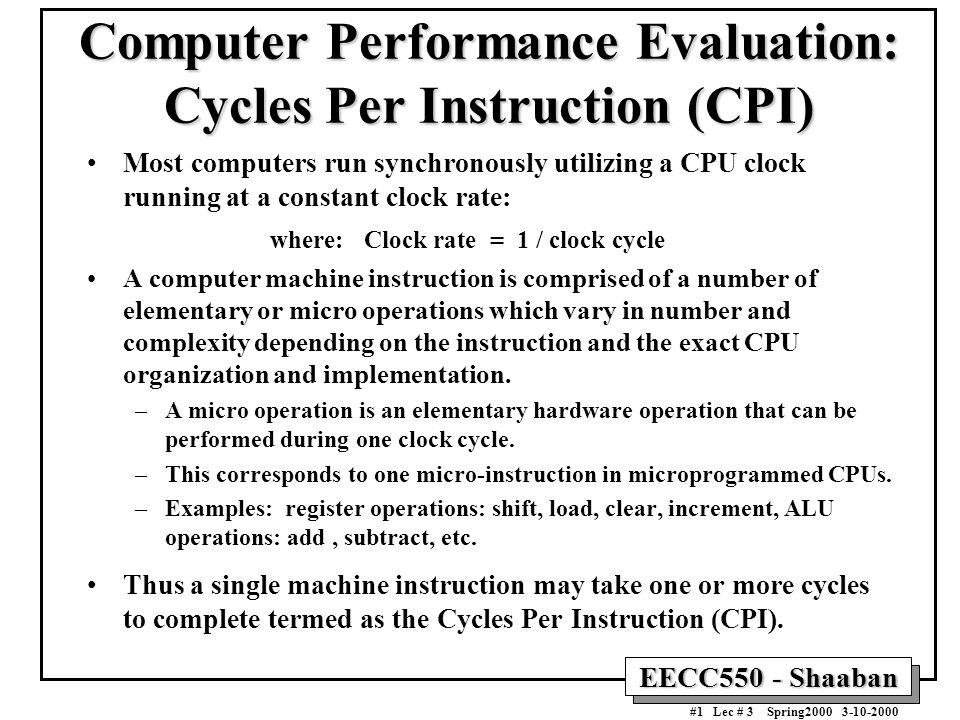

PPT - Computer Performance Evaluation: Cycles Per Instruction (CPI) PowerPoint Presentation - ID:195299