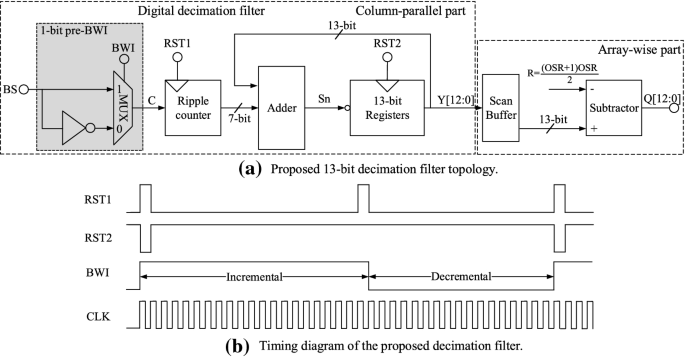

A Low-Area Low-Power Column-parallel Digital Decimation Filter Using 1-Bit Pre-BWI Topology for CMOS Image Sensor in 40-nm CMOS Process | SpringerLink

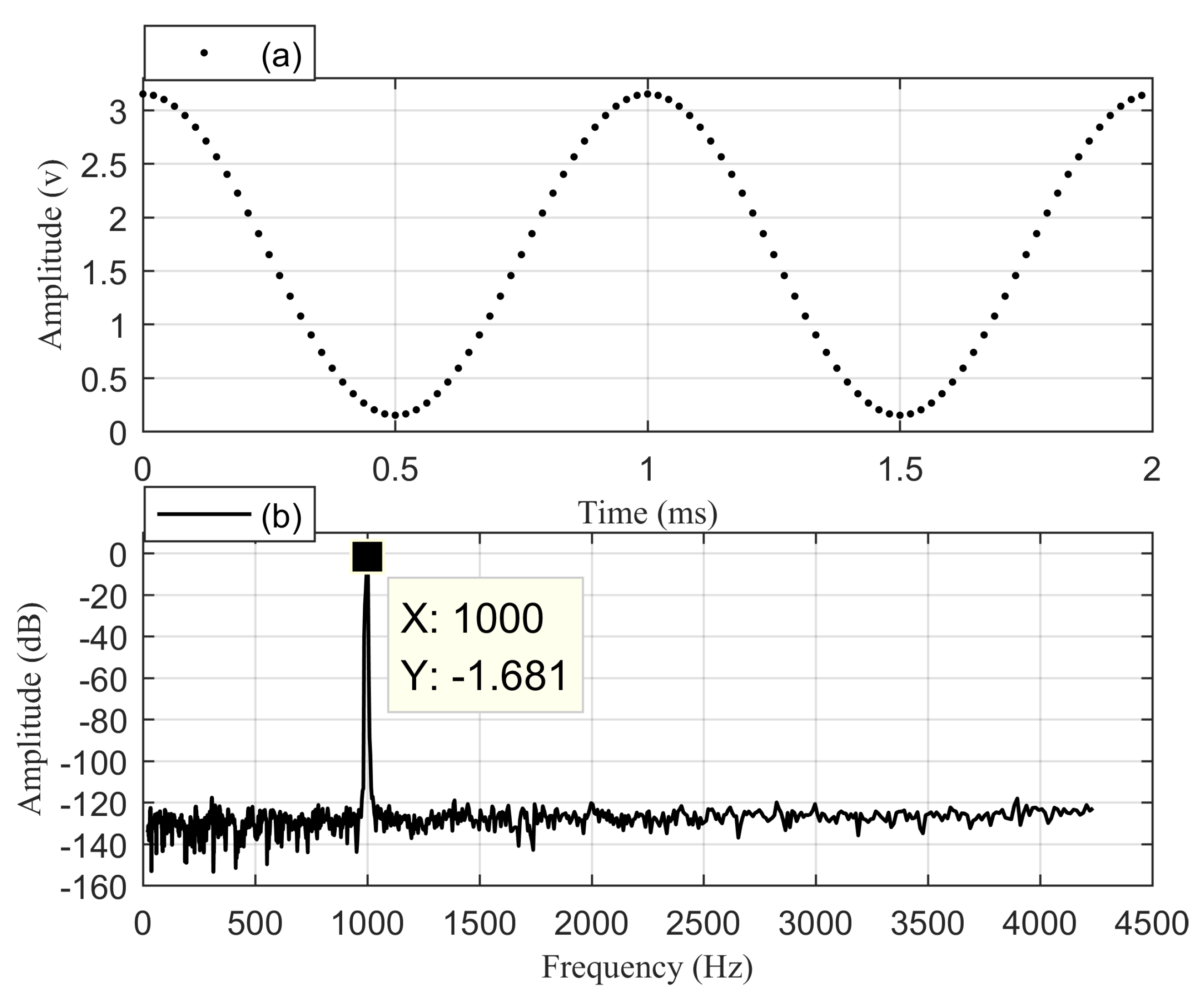

Antialiasing Filtering Considerations for High Precision SAR Analog-to-Digital Converters - ELE Times

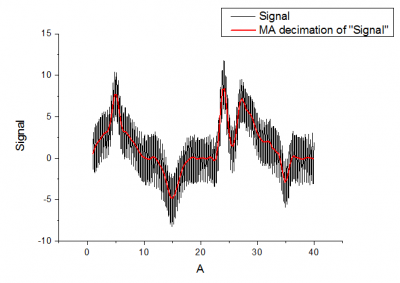

DSP Related on Twitter: "Rick Lyons' Optimizing the Half-band Filters in Multistage Decimation and Interpolation - https://t.co/SEJBtgDL9D https://t.co/yBiWBCCFSD" / Twitter